# 極紫外光微影-延續摩爾定律的重要技術

李建霖/臺灣大學電子工程學研究所/博士班研究生 蔡坤諭/臺灣大學電機工程學系/副教授

#### 一、 前言

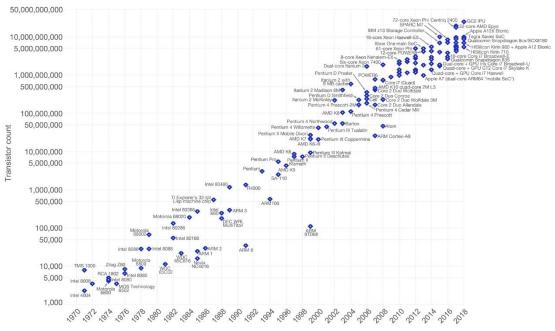

摩爾定律(Moore's Law)為描述計算硬體歷史上的一個長期趨勢:該定律為英 特爾公司的聯合創始人和名譽主席 Gordon E. Moore 博士長期觀察所提出的經驗 法則,意思是因半導體製程技術的提升,積體電路上可以相對低價置入的電晶體 數量大約每18個月至兩年增加一倍(如圖1)[1],又電晶體為執行運算的基本單元, 因此晶片性能也將提升一倍。該定律為 Moore 博士首先在 1965 年的一篇開創性 文章中提出[2],並於國際電子元件會議(IEDM)[3]、國際光電工程學會的微影技 術研討會(SPIE)[4]和國際固態電路研討會(ISSCC)[5]等重要的國際半導體領域會 議中持續探討至今。在所有演講中,微影(lithography)作為半導體製造中定義電路 圖像的關鍵製程,始終被認為是讓摩爾定律持續有效的關鍵技術和經濟因素之一。 甚至可以說,摩爾定律的過去和未來與微影技術的不斷發展和突破有著非常密切 的聯繫。而半導體製程中的微影技術可說是整個半導體工業相當關鍵的製程,因 為目前花費在微影製程的經費往往佔整個元件製作絕大部份的成本,而且這個比 例尚有逐年增加的趨勢,其重要性不言可喻。然而隨著摩爾定律逐漸走到物理極 限,傳統技術已無法繼續微縮晶片,此時極紫外光(EUV)微影機就在眾多技術下 突破重圍並且克服諸多困難被開發出來,繼續引領半導體產業邁入下一個摩爾定

### 律的十年。

Moore's Law – The number of transistors on integrated circuit chips (1971-2018)

Moore's law describes the empirical regularity that the number of transistors on integrated circuits doubles approximately every two years. This advancement is important as other aspects of technological progress – such as processing speed or the price of electronic products – are

Data source: Wikipedia (https://en.wikipedia.org/wiki/Transistor\_count)

The data visualization is available at OurWorldinData.org. There you find more visualizations and research on this topic.

Licensed under CC-BY-SA by the author Max Roser.

圖 1 摩爾定律示意圖:積體電路上可容納的電晶體數量約每隔 18 個月至 2 年便 會增加一倍。

## 光學微影技術

半導體產業之所以能快速發展,有很大一部分原因要歸功於光學微影技術, 1970 年代,利用汞燈產生的 g-line(436 nm 波長)的曝光系統問世時,光學微影就 因其高效率和產能開始成為半導體製造的主流。光學微影的解析度大致可以用下 列數學式表示

$$R = k_1 \frac{\lambda}{NA}$$

其中 R 代表光學微影的解析度極限; $\lambda$  表示在真空中光的波長;NA 代表成像系統的數值孔徑(Numerical Aperture); $k_1$  為包含製程相關因子的係數。爾後隨製程線寬不斷微縮,光源波長也從 i-line(365 nm 波長)到利用惰性氣體和鹵素分子結合激發的深紫外光(DUV)準分子雷射光源,如氟化氮(KrF)產生的 248 nm 波長和氟化氫(ArF)的 193 nm 波長等。

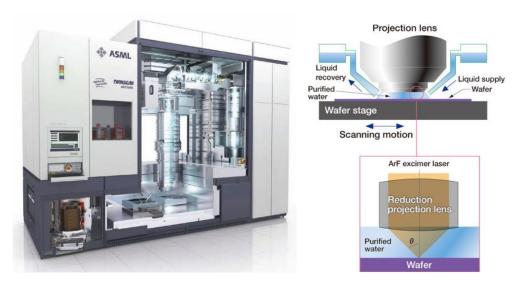

目前,領先的積體電路製造商所採用的光學投影式微影技術(OPL),使用DUV波段的曝光波長(波長=193 nm)、NA接近0.95的高數值孔徑投影透鏡、離軸照明和浸潤技術(n=1.437)[6],使得在一次曝光能中解析出密度高達45 nm的半間距的電路圖案。目前最先進的OPL系統和浸潤式透鏡的示意圖如圖2所示[7]。由於波的繞射,該系統最小可解析的半間距可用下列數學式表示

$$0.5 \frac{\lambda}{\text{NA}_{\text{p}} \cdot n \cdot (1 + \sigma)}$$

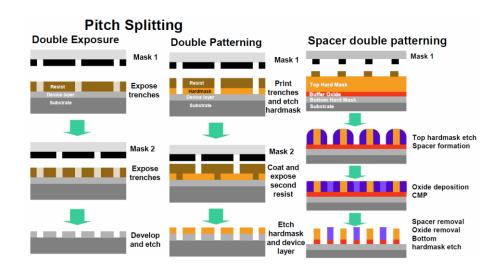

其中σ為部分同調係數,等於照明和投影光學元件之間的 NA 比(即σ=NAp/NAi)[8]。由於材料上的重大困難,進一步降低 DUV 波長和增加浸潤液的折射率在經濟上已被認為不可行,而 NAp 和σ也已提高到接近其理論極限(均為 1.0),因此,人們普遍認為 45 nm 半間距技術節點是單次曝光 OPL 的最後一個節點。後續技術節點將在維持曝光系統不變的情況下採用解析度增進技術(RET)和多重曝光技術(透過重複對準曝光提升同一層圖案密度的技術),使 OPL 解析度能繼續擴展到 32 nm 以下半間距技術節點。圖 3 所示為各種間距分割製造流程和

結果的示意圖[12]。目前直到 10/7 nm 的前瞻製程節點都在可接受的成本、效率及產能下採用了上述技術持續微縮製程。然而,在 7 nm 半間距節點以下,繼續增加 OPL 多重曝光次數造成製程複雜度和成本的提升將無法負荷,因此半導體產業只能再次更換波長更短的光源,如 13.5 nm 波長的極紫外光微影技術(EUVL),或非 OPL 技術,如電子東直寫微影技術(EBDWL)等無光罩曝光技術。最終,在產學研的合力研發下,EUVL 成功克服重重困難於 7/5 nm 技術節點開始肩負起晶片量產製造中的關鍵製程,並且可望在合理的成本下採用多重曝光技術將摩爾定律推進到 3 nm 以下技術節點。

圖 2 光學微影曝光機台及浸潤式鏡頭示意圖[7]

圖 3 三種間距分割製造流程:(左)雙重曝光,(中)雙重製像,(右)自對準雙重製像 [12]

### 三、 極紫外光微影技術

早在1980年代,美國及日本便開始研究利用 X 光波段(0.1-10 nm)進行微影 製程的技術,但因為 X 光難以聚焦的特性, X 光微影最初是使用鄰近曝光 (proximity printing)的方式。此方法由於光罩和晶圓上的圖案大小接近 1:1,因此需要搭配極高精確度的光罩生產技術才能發揮效益,即便研究後來轉向使用低能量 X 光投影式微影技術(Soft X-ray,使用波段基本上等同於現今的 EUV),但因為尚有許多困難如光源、多層反射膜等需要克服,加上當時主流的 OPL 技術已能應付量產需求,半導體產業目光便暫時專注於 OPL 相關技術上。直到近十幾年,OPL 在可預見的未來將走到極限,產業界極需尋找下一代微影技術,此時 EUVL 才又再次受到重視。

EUVL 基本上可以看作是 OPL 的延伸,其曝光波長大幅降低到極紫外光波段

(約10~121nm),因此同樣遵循前述的 OPL 解析度公式。而其最主要的區別為聚 焦用的鏡片,由於大多數材料在 EUV 波段下都具有很強的吸收性,因此傳統 OPL 所使用之折射透鏡和浸潤液都不適用。EUVL 光學系統通常以多層膜反射式鏡片 的形式實現。但由於每個多層膜鏡片在 EUV 波段下的反射率只有大約 70%,因 此光源功率一直都是 EUVL 量產的一大瓶頸,直到近年 ASML 回報的 EUVL 機 台光源功率終於超過 200W,才達到能夠量產的需求。除了光源以外,由於 EUVL 曝光劑量低造成的隨機效應,使得曝寫圖案的邊緣粗糙度(LER)往往不太理想, 需要開發新的光阻搭配整體製程調整使 LER 降低至可容許範圍。突破上述關卡 後,鏡片和光罩上的缺陷處理也是一大問題,因為 EUV 波長只有 13.5 nm,任何 奈米等級以上的灰塵或缺陷都會影響到生產良率,國內晶圓代工龍頭廠商也因為 搶先其他競爭對手處理好防塵的問題,而在導入 EUVL 技術於量產上奪得先機。

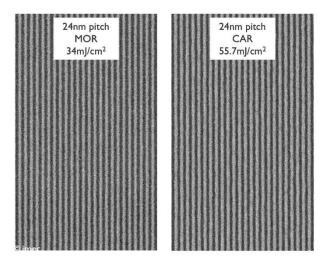

第一代量產型 EUV 機台的曝光波長為 13.5 nm, NA 在 0.25~0.35 之間,採用 6 個鏡面投影光學元件[9]。圖 4 和圖 5 為 ASML 所製造的 EUV 系統示意圖及最新世代所能達到的解析度 [7][10]。該曝光工具目前在 7/5 nm 技術節點上正式導入成為量產技術。

圖 4 ASML 極紫外光曝光系統示意圖[7]

圖 5 12 nm 半間距高密度線圖案之 SEM 圖[10]

#### 四、 結論

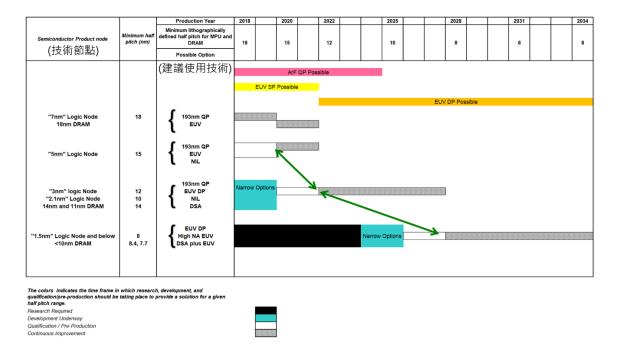

摩爾定律走至今日已過 50 年,如國際元件和系統藍圖(International Roadmap for Devices and Systems; IRDS) [11]所提供的資訊所示,更高 NA 的 EUV 機台搭配 RET 或多重曝光技術應可製造出數奈米半間距的圖案,則半導體量產中最要的設備之一或許將走到盡頭,再搭配半導體元件如全繞閘極式元件(gate-all-around)等研發及導入。以推進摩爾定律再符合經濟效益下微縮半導體製程而言或許即將結束,但半導體產業的 More than Moore 則剛開始嶄露頭角,諸如 3D 積體電路,異質整合晶片、5G 晶片等將繼續擴展半導體的應用及持續對人類帶來貢獻。

圖 6 國際元件和系統藍圖(International Roadmap for Devices and Systems; IRDS)

[11]根據不同技術節點所建議使用的微影技術。

### 參考連結

- [1] 維基百科: <a href="https://en.wikipedia.org/wiki/Moore%27s\_law">https://en.wikipedia.org/wiki/Moore%27s\_law</a>

- [2] G. Moore, "Cramming more components onto integrated circuits," Electronics 38(8), 1965

- [3] G. Moore, "Progress in digital integrated electronics," IEDM Tech Digest p. 11-13, 1975

- [4] G. Moore, "Lithography and the future of Moore's Law," Proc. SPIE Vol. 2437, May 1995

- [5] G. Moore, "No exponential is forever: But forever can be delayed!", ISSCC 2003

- [6] B. J. Lin, "Immersion lithography and its impact on semiconductor manufacturing," J. Microlithography, Microfabrication, and Microsystems, Vol. 3,

- No. 3, 377-395, Jul. 2004

- [7] ASML Images Customer Magazine, 2010.

- [8] A. K.-K. Wong, Resolution Enhancement Techniques in Optical Lithography, SPIE Press, 2001

- [9] C. Wagner et al., "EUV lithography at chipmakers has started: performance validation of ASML's NXE:3100," Proc. SPIE 7969, 79691F, 2011

- [10]IMEC: <a href="https://www.imec-int.com/en">https://www.imec-int.com/en</a>, "Imec demonstrates 24nm pitch lines with single exposure EUV lithography on ASML's NXE:3400B scanner"

- [11]International Roadmap for Devices and Systems, 2018 edition. Accessible at <a href="https://irds.ieee.org/">https://irds.ieee.org/</a>

- [12]H. Yaegashi et al., "Novel approaches to implement the self-aligned spacer double-patterning process toward 11-nm node and beyond," Proc. SPIE 7972, 79720B, 2011